Digital CMOS HMOS

Matra Harris semiconducteurs products are sold by description only. MHS reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that data sheets and other information in this publication are current before placing orders. Information contained in application notes is intended soley for general guidance; use of the information for user's specific application it at user's risk. Reference to products of other manufacturers are soley for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

Copyright © MHS 1983

(All rights reserved)

Printed in France - Edition 83-11-DI-C-76

Conception et impression Reflets Conseil - Nantes R.C. 83 B 181 - Tél. (40) 20.10.64

# CONTENTS

| General information  Alpha-numerix index of total product Devices by families Data sheet classifications IC handling procedure memory selection guide | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| CMOS memory                                                                                                                                           | 2  |

| CMOS gate arrays                                                                                                                                      | 3  |

| CMOS microprocessor                                                                                                                                   | 4  |

| HMOS microprocessor                                                                                                                                   | 5  |

| Microprocessor support systems                                                                                                                        | 6  |

| Telecommunication circuits                                                                                                                            | 7  |

| product assurance                                                                                                                                     | 8  |

| Ordering & packaging                                                                                                                                  | 9  |

| Order form for mask programmable parts                                                                                                                | 10 |

| Dice information                                                                                                                                      | 11 |

#### П

## **Total Product Index**

| NUM                                                               | ^   |

|-------------------------------------------------------------------|-----|

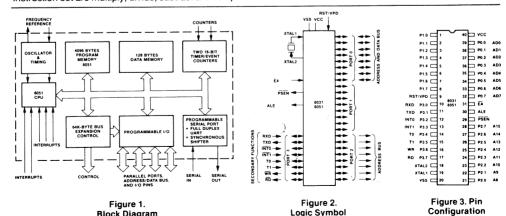

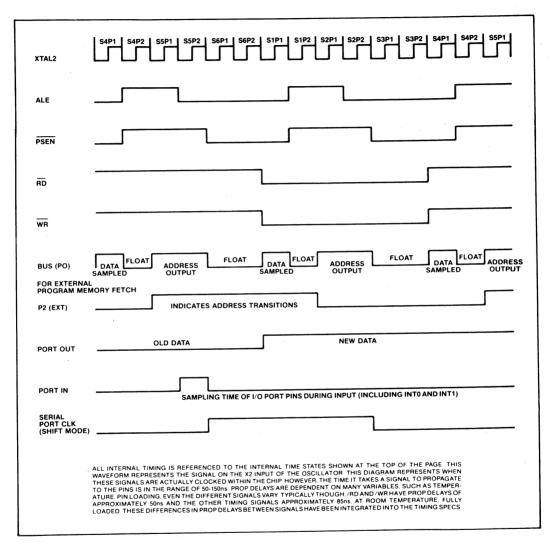

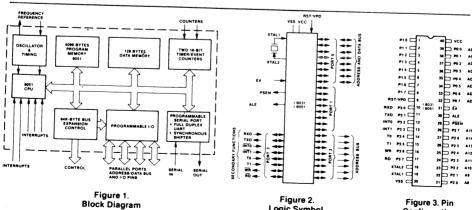

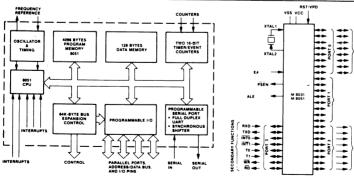

| 8031/8051 HMOS single component - 8 bit microcontrollers 5-       | . 3 |

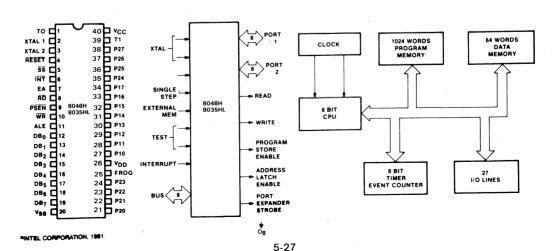

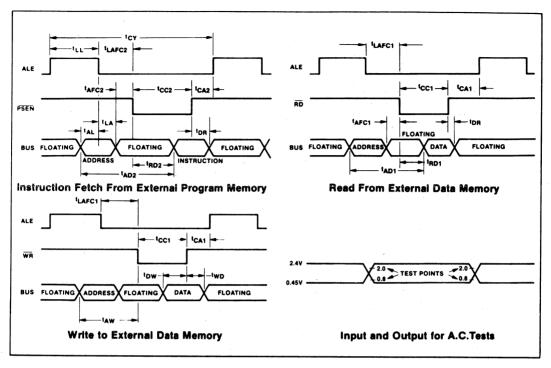

| 8035 HL/8048 H HMOS single component - 8 bit microcontrollers 5-2 | 27  |

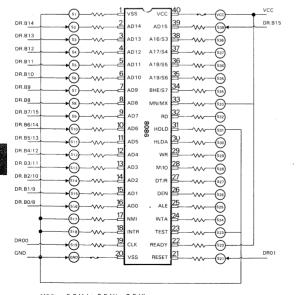

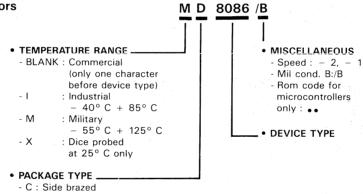

| 8086 16 bit HMOS microprocessor 5-6                               | 63  |

| 8088 8 bit HMOS microprocessor 5-6                                | 68  |

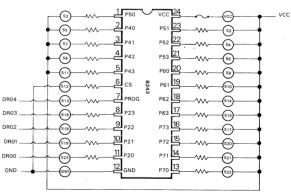

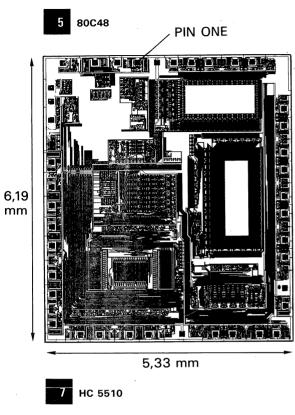

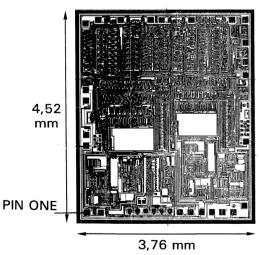

| 80C35/80C48 CMOS single component - 8 bit microcontrollers 4-     | -3  |

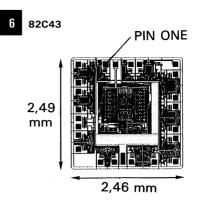

| 82C43 CMOS I/O expander for MCS 48 family 4-                      | 15  |

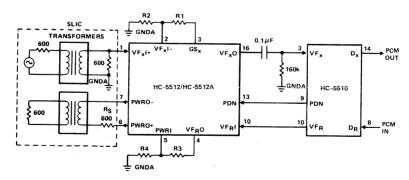

| HC 5510/5511 Monolithic CODECS 7-                                 | .3  |

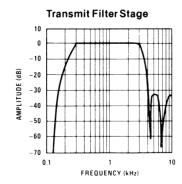

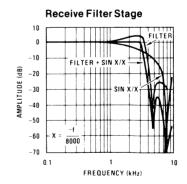

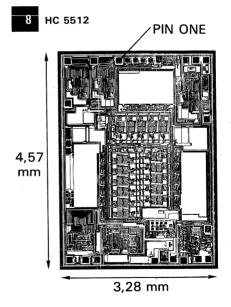

| HC 5512/12A PCM monolithic filter 7-                              | 12  |

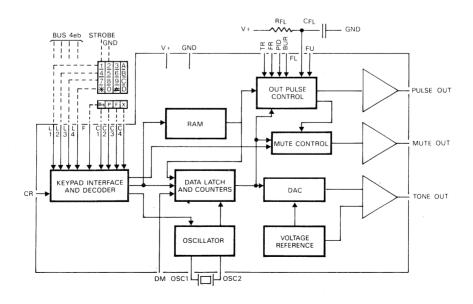

| HC 5541A Pulse/Tone dialer 7-                                     | 19  |

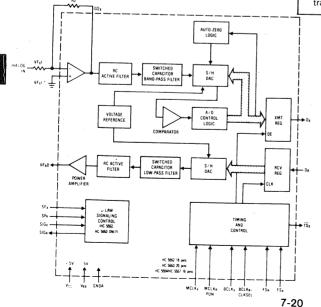

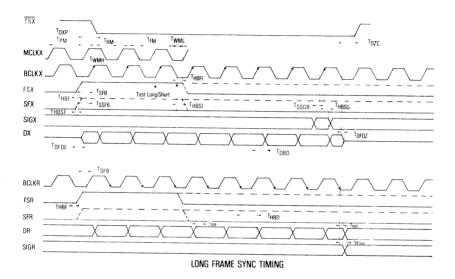

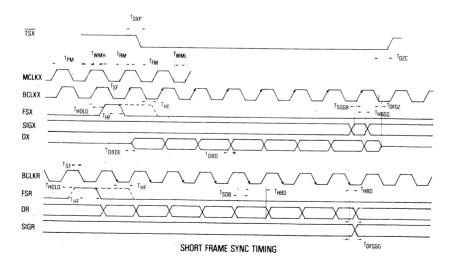

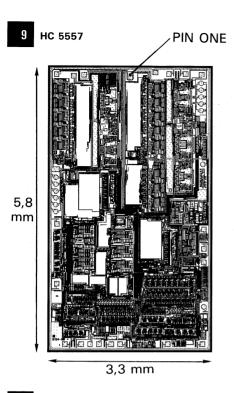

| HC 5552-3-4-7 Cofidec 7-2                                         | 20  |

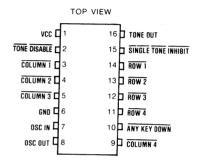

| HC 5589 DTMF generator 7-2                                        | 29  |

| HM 6116 $2K \times 8$ CMOS RAM 2-                                 | .5  |

| HM 6504 $4096 \times 1$ CMOS RAM $2-$                             | 11  |

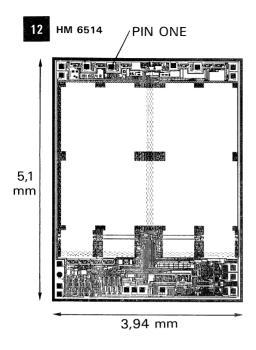

| HM 6514 $1024 \times 4$ CMOS RAM $2-2$                            | 21  |

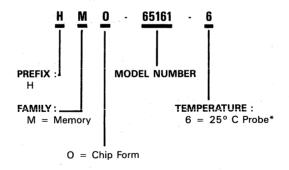

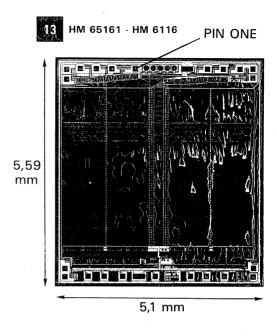

| HM 65161 2048 $\times$ 8 CMOS RAM 2-3                             | 31  |

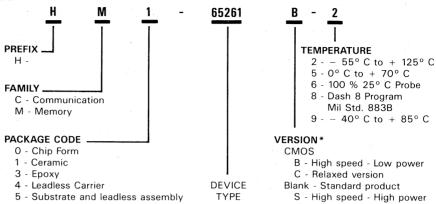

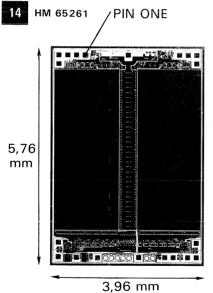

| HM 65261 $16K \times 1$ CMOS RAM $2-3$                            | 37  |

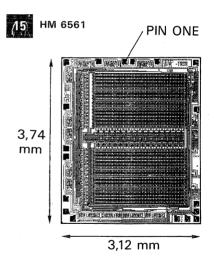

| HM 6561 256 $\times$ 4 CMOS RAM 2-2                               | 43  |

| HM 6564 8K $\times$ 8, 16K $\times$ 4 CMOS RAM $_{2-\xi}$         |     |

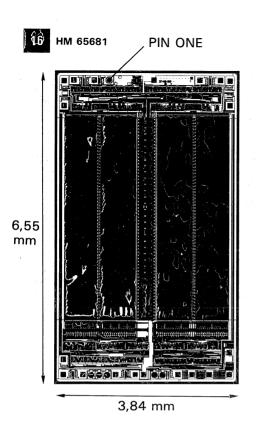

| HM 65681 $4K \times 4$ CMOS RAM $2-6$                             |     |

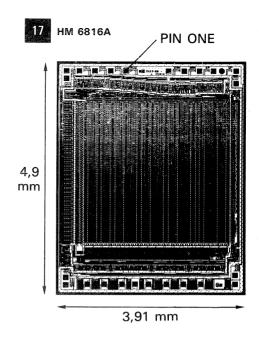

| HM 6816A 2K $\times$ 8 CMOS EEPROM 2-6                            |     |

| MA 0250 ) 3 <sub>3</sub> -                                        |     |

| MA 0400/0800                                                      | -   |

## **Devices by Families**

| CMOS RAM     | Page   |

|--------------|--------|

| HM 6116      | 2-5    |

| HM 6504      | 2-11   |

| HM 6514      | 2-21   |

| HM 65161     | 2-31   |

| HM 65261     | 2-37   |

| HM 6561      | 2-43   |

| HM 6564      | 2-50   |

| HM 65681     | 2-60   |

| HM 6816A     | 2-61   |

| CMOS μP      | Page   |

| 80C35/80C48  | 4-3    |

| 82C43        | 4-15   |

|              |        |

| HMOS μP      | Page   |

| 8031/8051    | 5-3    |

| 8035HL/8048H | 5-27   |

| 8086         | . 5-63 |

|              |        |

| 8088         | 5-68   |

| Telecommunication circui | ts Page |

|--------------------------|---------|

| HC 5510/5511             | 7-3     |

| HC 5512/12A              | 7-12    |

| HC 5541A                 | 7-19    |

| HC 5552 - 3 - 4 - 7      | 7-20    |

| HC 5589                  | 7-29    |

| CMOS gate arrays         | Page    |

| MA 0250 - 400 - 800 - 12 | 00 3-3  |

## **Data Sheet Classifications**

| CLASSIFICATION                       | PRODUCT STAGE                 | DISCLAIMERS                                                                                                                                 |

|--------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Preview DATA SHEET                   | Formative or<br>Design        | This document contains the design specifications for product under development. Specifications may be changed in any manner without notice. |

| Advance<br>Information<br>DATA SHEET | Sampling or<br>Pre-Production | This is advanced information, and specifications are subject to change without notice.                                                      |

| Preliminary DATA SHEET               | First Production              | Supplementary data may be published at a later date.                                                                                        |

|                                      |                               | MHS reserves the right to make changes at any time without notice, in order to improve design and supply the best product possible.         |

## I. C. Handling Procedures

I.C. processes produce circuits more rugged than similar ones. However, no semiconductor is immune from damage resulting from the sudden application of many thousands of volts of static electricity. While the phenomenon of catastrophic failure of devices containing MOS transistors or capacitors is well known, even bipolar circuits can be damaged by static discharge, with altered electrical properties and diminished reliability. None of the common I.C internal protection networks operate quickly enough to positively prevent damage.

It is suggested that all semiconductors be handled, tested, and installed using standard "MOS handling techniques" of proper grounding of personnel and equipment. Parts and subassemblies should not be in contact with untreated plastic bags or wrapping material. High impedance I.C. inputs wired to a P.C. connector should have a path to ground on the card.

#### **HANDLING RULES**

Since the introduction of integrated circuits with MOS structures and high quality junctions, a safe and effective means of handling these devices has been of primary importance. One method employed to protect gate oxide structures is to incorporate input protection diodes directly on the monolithic chip. However, there is no completely foolproof system of chip input protection in existance in the industry. In addition most compensation networks in linear circuits are located at high impedance nodes, where protection networks would disturb normal circuit operation. If static discharge occurs at sufficient magnitude (2 kV or more), some damage or degradation will usually occur. It has been found that handling equipment and personnel can generate static potentials in excess of 10 KV in a low humidity environment; thus it becomes necessary for additional measures to be implemented to eliminate or reduce static charge. It is evident, therefore, that proper handling procedures or rules should be adopted.

Elimination or reduction of static charge can be accomplished as follows:

- Use conductive work stations. Metallic or conductive plastic\* tops on work benches connected to ground help eliminate static build-up.

- Ground all handling equipment.

- Ground all handling personnel with a conductive bracelet through 1-M ohm to ground. The 1-M ohm resistor will prevent electroshock injury to personnel.

- Smocks, clothing, and especially shoes

of certain insulating materials (notably

nylon) should not be worn in areas

where devices are handled. These

materials, highly dielectric in nature, will

hold, or aid, in the generation of a static

change. Where they cannot be eliminated natural materials such as cotton

etc. should be used to minimize charge

generation capacity.

- Control relative humidity to as high as a level as practical (RH 50 %).

- lonized air blowers reduce charge buildup in areas where grounding is not possible or desirable.

- Devices should be in conductive carriers during all phases of transport. Leads may be shorted by tubular metallic carriers, conductive foam or foil.

- In automated handling equipment, the belts, chutes, or other surfaces should be of conducting material. If this is not possible, ionized air blowers may be a good alternative.

<sup>\*</sup> Supplier 3M Company "Velostat".

|               |                          | П              |              |              |      |           | _         |        |                    |           | т            |              |                   |              | <u>.</u> |                 |            |             |             |             |            |             |

|---------------|--------------------------|----------------|--------------|--------------|------|-----------|-----------|--------|--------------------|-----------|--------------|--------------|-------------------|--------------|----------|-----------------|------------|-------------|-------------|-------------|------------|-------------|

|               | SIZE & ORGANI-<br>ZATION | ≠              |              | 256 × 4      |      |           |           | ŧ      | -                  | ,         |              | 4            |                   | ₹<br>×<br>4  |          | 168             | 2K × 8     |             | 16K × 1     |             | 4×<br>×    | 8 64<br>8 8 |

|               | TYPE PI                  | CMOS           |              | NMOS         |      |           |           | Civico | NA<br>OA           |           |              | CMOS         |                   | SOWN         |          | CMOS            |            | CMOS        | NMOS        | CMOS        | NMOS       | CMOS        |

|               | i<br>MHS                 | 18 6561        | 6            | 8            | 22   | - ;       | 18 6504   | 20     | 18                 | 3         | 18 6514      | 3            | 18                | 20           | 22       | 24 65           | 24         | 24 65261    | 24          | 24 6568     | 24         | 40 6        |

| RIS           | HAR                      | 51             | 9112         | 2112         | 21   | 9101      | -         |        | 91                 | 91        | T            | +            | ဖွဖ               | 9 9          | 9        | 6516            | -   -      | 261         | $\dashv$    | 681         |            | 6564        |

|               | AMI                      |                | 12           | 12           | 2 =  | 01        | H         | -      | 9145 40<br>9147 21 | 6         | $\dashv$     | +            | 9124 21<br>9135   | 9148         | 9130     |                 | +          |             | -           |             |            |             |

|               | EA                       |                | 2112         | 2111         | 2101 | L         | Н         | _      | 4017<br>2147       | +         | -            | +            | 2114              | +            |          | +               | +          |             |             | _           |            |             |

|               |                          | -              | 72           | =            | 2    | -         | 8         | _      | 21                 | +         | 841          | +            | _                 | +            | +        | -               |            |             | <u></u>     | -           | 8          |             |

|               | FUJIT                    | -              | +            | +            | 4    |           | 8404      |        | 2147               | 4         | 4            | $\downarrow$ | _                 | 4            | 4        | S MB            | MB<br>8128 |             | MB<br>8167  |             | MB<br>8168 |             |

|               | GI                       |                |              | -            | 4256 | -         |           |        | 44                 | 4200      |              | +            | 4 12              | 4            | 4        | _               |            |             |             |             |            |             |

|               | GTE                      | _              | $\dashv$     | -            | -    | -         | 4         | +      | 4104<br>4200<br>4  | 4         | 4.0          | 4            | 2114<br>4804<br>6 |              |          |                 |            | _           |             |             |            |             |

| н             | HITAC                    |                | 4            | -            | 4    |           | 4315      | -      | 6147<br>4847       | 4         | 6148<br>4334 | 4            | 472114<br>6148    |              |          | 6116            | 1          | HM<br>6167  |             | HM<br>6168  |            |             |

| s<br>         | INMO                     |                | _            | -            | -    | -         | -         | L      |                    | -         |              | 1            | ,                 |              | -        |                 |            |             | MS<br>1400  |             | MS<br>1420 |             |

|               | IDT                      |                | N            | N            |      |           | _         |        |                    |           |              | 1            |                   | _            |          | 6116<br>116     |            | IDT<br>6167 |             | 1DT<br>6168 |            |             |

| -             | INTE                     | _              | 2112         | 2111         | 2101 | ┺         | L         | +-     | 2141               | _         |              |              | 2114<br>2148      | 2142         |          |                 | 21821      | -           | 2167        |             |            |             |

|               | INTER                    | 6561           |              |              |      | +-        | 6504      |        | 214/               |           | 6514         |              | 2148              |              |          |                 |            |             |             |             |            |             |

| O POWE<br>EMS | MICR                     |                |              |              |      |           | 6504      |        |                    |           | 6514         |              |                   |              |          |                 |            |             |             |             |            |             |

| iL            | МІТЕ                     |                |              |              |      |           |           |        |                    |           | 21C14        |              |                   |              |          |                 |            |             |             |             |            |             |

| UBISHI        | MITS                     |                |              |              |      |           |           |        |                    |           | 58981        |              |                   |              |          |                 | M<br>58725 |             |             |             |            |             |

| TEK           | Mos                      |                |              |              |      |           |           | 2      | 2147               |           |              |              | 2148              |              |          |                 | 4802       |             | 4167        |             |            |             |

| OROLA         | мот                      |                |              |              |      |           | 6504      | 21/4   | 714/               |           | 6514         |              | 2114<br>2148      |              |          | MCM<br>65116    |            |             | MCM<br>2167 |             |            |             |

| ONAL          | NATI                     | 74C921<br>6552 | 2112         | 2111         | 2101 | 2         | 6504      | 2141   | 2147               |           | 6514<br>6848 |              | 2148              | 2141<br>2142 |          | 0116            |            |             |             |             |            |             |

|               | NEC                      |                |              | 2111         | 2101 |           |           | 4104   | 2147               |           | 444          | 445          | 2114              |              |          | μPD<br>446      |            | μPD<br>2167 |             | μPD<br>2168 |            |             |

|               | окі                      |                |              |              |      |           | 5104      |        |                    |           | 5114<br>5115 |              | 2114              |              |          | MSM<br>5128     | 2128       | Ė           |             |             |            |             |

|               | RCA                      |                | 4112         | 4111         | 4101 |           |           |        |                    |           | 5114         |              |                   |              |          | CDM<br>6116E    | T          |             |             |             |            |             |

| NETICS        | SIGN                     |                | 2112<br>2606 | 2111         | 2101 | 1         |           | 2613   |                    |           |              |              | 2614              |              |          | -               |            |             |             | T           |            |             |

| ID STATE      | SOL                      |                |              |              |      | T         | T         | T      |                    |           |              |              |                   |              |          |                 |            | T           |             |             | +          |             |

| IERTEK        | SYN                      |                | 2112         | 2111<br>2112 | 2101 | T         | T         | 2147   |                    | T         |              |              | 2114              | 2142         |          |                 |            | $\vdash$    |             | +           | -          | -           |

|               | TI                       |                | 4043         | 4042         | 4039 | 1         | $\dagger$ | -      | 4044               |           |              |              | 4045<br>4047      | 13           |          |                 | 4016       |             | $\dagger$   | +           |            | _           |

| ніва          | тоѕ                      |                |              |              |      | 5504      | 000       | 315D   |                    |           | 4            |              | 314A              |              |          | 5516<br>5517-18 | 6 2016     |             |             | -           | +          | H           |

| )G            | ZILO                     |                |              |              |      | $\dagger$ | Ť         | _      | 6104               | $\dagger$ | Ť            | Ť            | Ĺ                 |              |          | 18 6            | 1 6        | +           | $\dagger$   | +           | +          | H           |

##

ω

WORDS

65536 32768

# CMOS memory 2

| roa         |  |  |

|-------------|--|--|

| uct         |  |  |

| ind         |  |  |

| ex          |  |  |

|             |  |  |

| <b>Z-</b> Z |  |  |

Symbols and abbreviations 2-3

Product information 2-5

## 9

## **Product Index**

|          |                                         | PAGE |

|----------|-----------------------------------------|------|

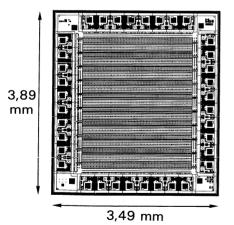

| HM 6116  | 2K × 8 CMOS RAM                         | 2-5  |

| HM 6504  | 4096 × 1 CMOS RAM                       | 2-11 |

| HM 6514  | 1024 × 4 CMOS RAM                       | 2-21 |

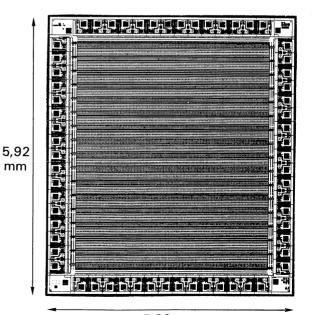

| HM 65161 | 2048 × 8 CMOS RAM                       | 2-31 |

| HM 65261 | 16K × 1 CMOS RAM                        | 2-37 |

| HM 6561  | $256 \times 4$ CMOS RAM                 | 2-43 |

| HM 6564  | $8K \times 8$ , $16K \times 4$ CMOS RAM | 2-50 |

| HM 65681 | 4K × 4 CMOS RAM                         | 2-60 |

| HM 6816A | 2K × 8 CMOS EEPROM                      | 2-61 |

#### **ABSOLUTE MAXIMUM RATINGS**

As with all semiconductors, stresses listed under "Absolute Maximum Ratings" may be applied to devices (one at a time) without resulting in permanent damage. This is a stress rating only. Exposure to absolute maximum rating conditions for extended periods may affect devices reliability. The conditions listed under "Electrical Characteristics" are the only conditions recommended for satisfactory operation.

## **Symbols and Abbreviations**

This data book utilizes a new set of specification nomenclature. This new format is an IEEE and JEDEC supported standard for semiconductor memories. It is intented to clarify the symbols, abbreviations and definitions, and to make all memory data sheets consistent. We believe that, once acclimated, you will find this standardized format easy to read and use.

## ELECTRICAL PARAMETER ABBREVIATIONS

All abbreviations use upper case letters with no subscripts. The initial symbol is one of these four characters:

- V (Voltage)

- I (Current)

- P (Power)

- C (Capacitance)

The second letter specifies input (0) or output (0), and the third letter indicates the high (H), low (L) or off (Z) state of the pin during measurements. Examples:

VIL — Input Low Voltage IOZ — Output Leakage Current

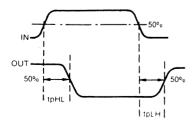

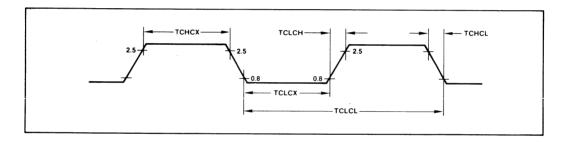

## TIMING PARAMETER ABBREVIATIONS

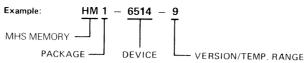

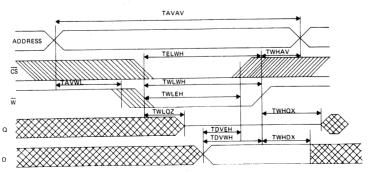

All timing abbreviations use upper case characters with no subscripts. The initial character is always T and is followed by four descriptors. These characters specify two signal points arranged in a "from-to" sequence that define a timing interval. The two descriptors for each signal point specify the signal name and the signal transitions. Thus the format is:

Signal name from which interval is defined

Transition direction for first signal

Signal name to which interval is defined

Transition direction for second signal

TXXXX

#### Signal Definitions:

- A = Address

- D = Data In

- Q = Data Out

- W = Write Enable

- E = Chip Enable

- S = Chip Select

- G = Output Enable

## Transition Définitions :

- H = Transition to High

- L = Transition to Low

- V = Transition to Valid

- X = Transition to Invalid or Don't Care

- Z = Transition to Off (High Impedance)

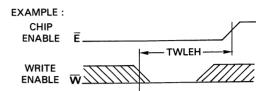

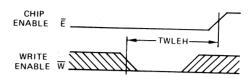

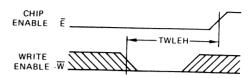

The example shows Write pulse setup time defined as TWLEH - Time from Write enable Low to chip Enable High.

#### **TIMING LIMITS**

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address set-up time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

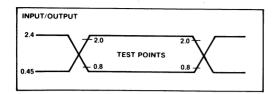

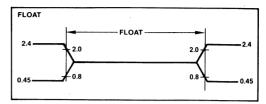

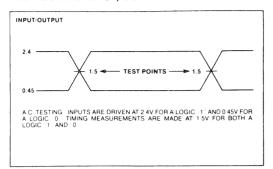

#### **WAVEFORMS**

| WAVE-<br>FORM<br>SYMBOL | INPUT                                 | ОИТРИТ                     |

|-------------------------|---------------------------------------|----------------------------|

|                         | MUST BE<br>VALID                      | WILL BE<br>VALID           |

|                         | CHANGE<br>FROM H TO L                 | WILL CHANGE<br>FROM H TO L |

|                         | CHANGE<br>FROM L TO H                 | WILL CHANGE<br>FROM L TO H |

| <b>XX</b>               | DON'T CARE<br>ANY CHANGE<br>PERMITTED | CHANGING<br>STATE UNKNOWN  |

| $\rightarrow$           |                                       | HIGH<br>IMPEDANCE          |

# data sheet

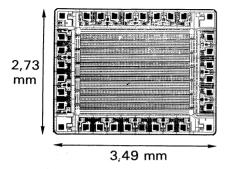

## HM 6116/6116 L 2K × 8 CMOS STATIC RAM

#### Features

- .ASYNCHRONOUS

- .FAST ACCESS: 120 ns max

- .STAND BY CURRENT: 100 µA max

- .OPERATING SUPPLY CURRENT : 60 mA max

- ,DATA RETENTION\* : 2 V min a 50  $\mu$ A max

- STATIC MEMORY CELL

- .INDUSTRY STANDARD PIN OUT

- .HIGH OUTPUT DRIVE: 5 std TTL LS/Load

- SINGLE SUPPLY : 5 V Vcc

- .TTL COMPATIBLE INPUTS AND OUTPUTS

- .WIDE TEMPERATURE RANGE

- .GATED INPUT BUFFER

## Description

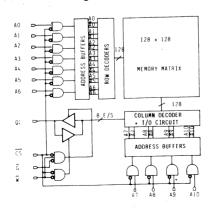

- .The HM 6116 is a 16384 bits static random access memory organized as 2048 words by 8 bits using CMOS technology and operates from the single 5 V supply.

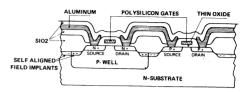

- .The HM 6116 use "state of the art" MHS technology: the scaled self aligned junction isolation featuring low stand by current and fast address time.

- .The HM 6116 features fully static operation requiring no external clocks or timing strobes, equal access and cycle times.

- .8 product available, 100 % screened following MIL STD 883 class B.

- \* Data retention mode for L version.

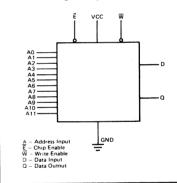

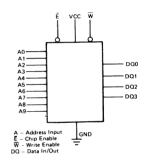

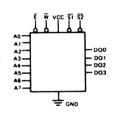

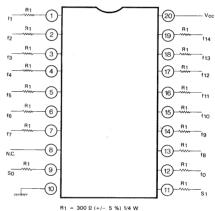

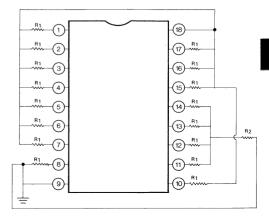

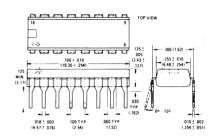

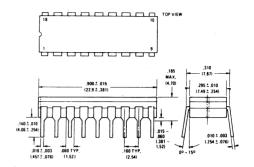

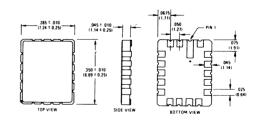

#### Pinout

A Address input

DO Data Input/Output

CS Chip Select

G Output Enable

W Write Enable

LCC

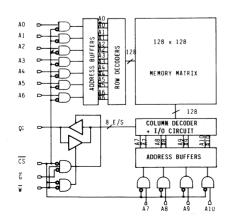

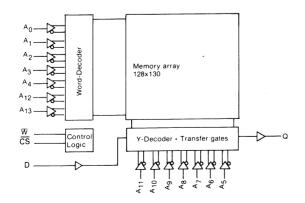

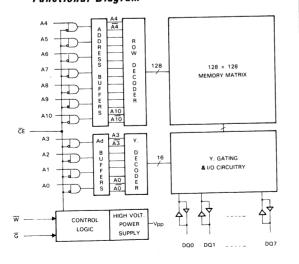

## Functional Diagram

## Logic Symbol

#### ABSOLUTE MAXIMUM RATINGS • OPERATING RANGE Operating Voltage Range 4.5V to 5.5V Operating Temperature · 55° to + 125° Supply voltage (Vcc·GND) · 0.3V\* to + 7V Input or Output Voltage Applied : (GND-0.3V\*) to : (Vcc+0.3V) Storage temperature : 65° C to + 150° C Military (- 2) Industrial (- 9) Commercial (- 5) 4.5V to 5.5V 4.5V to 5.5V - 40 ° to + 85° 0° to 70°

#### **ELECTRICAL CHARACTERISTICS**

#### DC PARAMETERS

| SYMBOL     | PARAMETER                        | 6116<br>-5 | 6116<br>L-5 | 6116<br>-2 | 6116 L<br>-2 | 6116<br>-9 | 6116 L<br>-9 | UNIT | VALUE |

|------------|----------------------------------|------------|-------------|------------|--------------|------------|--------------|------|-------|

| ICCSB (1)  | standby supply current           | 3          | 2           | 5          | 4.5          | 4.5        | 4.0          | mA   | max   |

| ICCSB1 (2) | standby supply current           | 2000       | 100         | 3000       | 1500         | 1000       | 500          | μА   | max   |

| ICCOP (3)  | power supply current             | 70         | 60          | 85         | 80           | 80         | 70           | mA   | max   |

| ICC (4)    | average operating supply current | 70         | 60          | 85         | 80           | 80         | 70           | mA   | max   |

| II/O (5)   | input/output/package current     | ± 2        | ± 2         | ± 10       | ± 5          | ± 5        | ± 2          | μА   | max   |

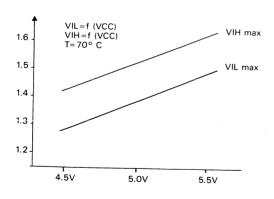

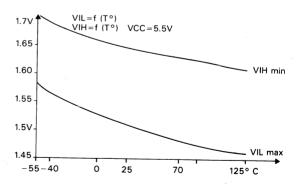

| VIL (6)    | input low voltage                | 0.8        | 0.8         | 0.8        | 0.8          | 0.8        | 0.8          | V    | max   |

| VIH (6)    | input high voltage               | 2.2        | 2.2         | VCC-2      | VCC-2        | 2.2        | 2.2          | V    | min   |

| VOL (7)    | output low voltage               | 0.4        | 0.4         | 0.4        | 0.4          | 0.4        | 0.4          | · V  | max   |

| VOH (7)    | output high voltage              | 2.4        | 2.4         | 2.4        | 2.4          | 2.4        | 2.4          | v    | min   |

| CI (8)     | input capitance                  | -8         | 8           | . 8        | 8            | 8          | 8            | PF   | max   |

| CO (8)     | input/output capitance           | 10         | 10          | 10         | 10           | 10         | 10           | PF   | max   |

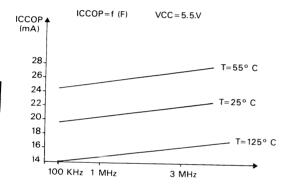

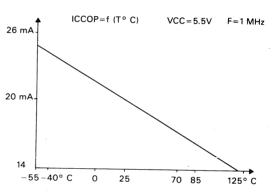

NOTE 1 : CS = VIH ; Iio = 0 ; input gating NOTE 2 :  $CS = VCC \cdot 0.3V$  ; Iio = 0 NOTE 3 : ICCOP with a duty cycle = 100 %; VI = VCC or GND; IO = 0; typical derating = 5 mA/MHz increase in ICCOP NOTE 4 : CS = VIL, IIVO = 0; addresses and data inputs level = VCC or GND NOTE 5 : VCC = 5V ; VIN = CND to VCC NOTE 6 : VIH max = VCC + 0.3V ; VIL min = -IV pulse width 50 ns NOTE 7 : IOL = 4 mA; IOH = -1 mA NOTE 8 : capacitance sampled and guaranteed not 100 % tested TA =  $25^{\circ}$  C, f = 1 MHz

#### AC PARAMETERS

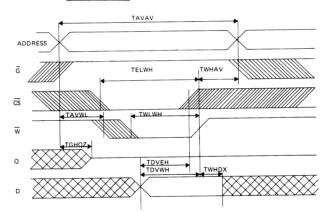

#### WRITE CYCLE

| SYMBOL | PARAMETER (1)                        | 6116<br>-5 | 6116<br>L-5 | 6116<br>-2 | 6116 L<br>-2 | 6116<br>-9 | 6116 L<br>-9 | UNIT | VALUE |

|--------|--------------------------------------|------------|-------------|------------|--------------|------------|--------------|------|-------|

| TAVAV  | write cycle time                     | 120        | 120         | 120        | 120          | 120        | 120          | ns   | min   |

| TELWH  | chip selection to end of write       | 70         | 70          | 70         | 70           | 70         | 70           | ns   | min   |

| TAVWH  | address valid to end of write        | 105        | 105         | 105        | 105          | 105        | 105          | ns   | min   |

| TAVWL  | address setup time                   | 20         | 20          | 20         | 20           | 20         | 20           | ns   | min   |

| TWLWH  | write pulse width                    | 70         | 70          | 70         | 70           | 70         | 70           | ns   | min   |

| TWHAV  | write recovery time                  | 5          | 5           | . 5        | 5            | 5          | - 5          | ns   | max   |

| TGHOZ  | output enable to output in high Z    | 40         | . 40        | 40         | 40           | 40         | 40           | ns   | max   |

| TWLOZ  | write low to output in high Z        | 50         | 50          | . 50       | 50           | 50         | 50           | ns   | min   |

| TDVWH  | input data valid to write high       | 35         | 35          | 35         | 35           | 35         | 35           | ns   | min   |

| TWHDX  | data hold from write time            | 5          | 5           | 5          | 5            | 5          | 5            | ns   | min   |

| XDHWT  | output active from end of write      | 5          | 5           | 5          | 5            | 5          | 5            | ns   | min   |

| TWLEH  | write low to chip select high        | 70         | 70          | . 70       | 70           | 70         | 70           | ns   | min   |

| TDVEH  | input data valid to chip select high | 35         | 35          | 35         | 35           | 35         | 35           | ns   | min   |

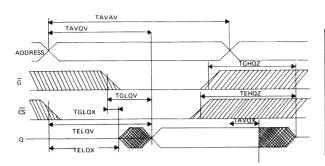

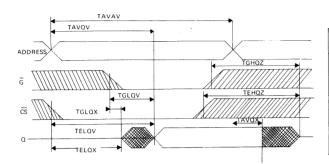

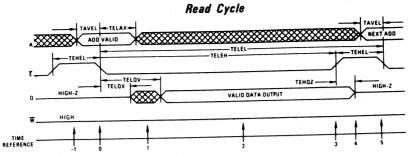

#### READ CYCLE

| SYMBOL | PARAMETER (1)                          | 6116<br>-5 | 6116<br>L-5 | 6116<br>-2 | 6116 L<br>-2 | 6116<br>-9 | 6116 L<br>-9 | UNIT | VALUE |

|--------|----------------------------------------|------------|-------------|------------|--------------|------------|--------------|------|-------|

| TAVAV  | read cycle time                        | 120        | 120         | 120        | 120          | 120        | 120          | ns   | min   |

| TAVQV  | address access time                    | 120        | 120         | 120        | 120          | 120        | 120          | ns   | max   |

| TELQV  | chip select access time                | 120        | 120         | 120        | 120          | . 120      | 120          | ns   | max   |

| TELQX  | chip select low to active output       | 10         | 10          | 10         | 10           | 10         | 10           | ns   | min   |

| TGLQV  | output enable to output valid time     | 80         | 80          | 80         | 80           | 80         | 80           | ns   | max   |

| TGLQX  | output enable to output in low Z time  | 10         | 10          | 10         | 10           | 10         | 10           | ns   | min   |

| TEHQZ  | chip select disable time               | 40         | 40          | 40         | 40           | 40         | 40           | ns   | max   |

| TGHOZ  | output enable to output in high Z time | 40         | 40          | 40         | 40           | 40         | 40           | ns   | max   |

| TAVQX  | output holdtime from address change    | 10         | 10          | 10         | 10           | 10         | 10           | ns   | min   |

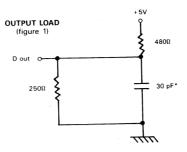

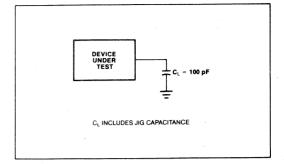

NOTE 1: LOAD: 100 pf (including JIG) AND TTL GATE

## Specifications HM-6116 - HM-6116L

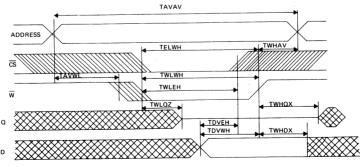

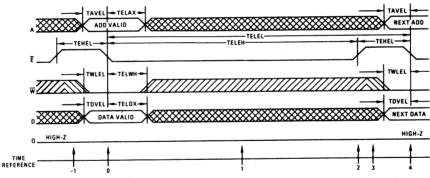

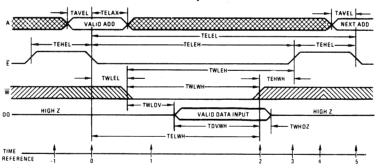

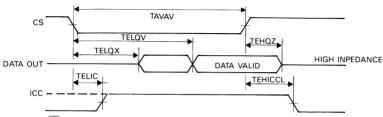

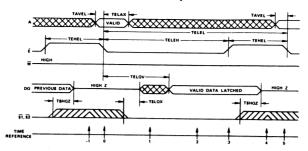

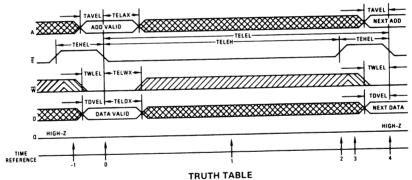

#### 1. READ CYCLE

TRUTH TABLE :

| cs | Ğ | w | D     | Q     | POWER SUPPLY<br>CURRENT | MODE                    |

|----|---|---|-------|-------|-------------------------|-------------------------|

| н  | х | × | Z     | Z     | ICCSB                   | CS=VIH<br>DESELECT      |

| н  | × | × | z     | Z     | ICCSB1                  | CS >Vcc-0.3<br>DESELECT |

| L  | L | н | Z     | VALID | ICC                     | READ                    |

| L  | н | L | VALID | Z     | ICC                     | WRITE                   |

| L  | L | L | VALID | Ž     | ICC                     | WRITE                   |

| L  | Н | н | z     | Z     | ICC                     | DESELECT                |

NOTE : W IS HIGH FOR A READ CYCLE

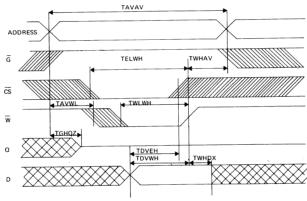

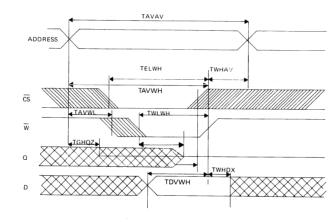

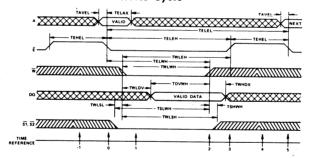

#### 3. WRITE CYCLE TIME 1

This write cycle time is recommended for continuous writing.

$\widetilde{G}$  = VIH during this write cycle.

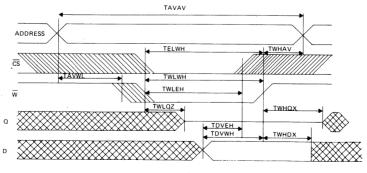

#### 3. WRITE CYCLE TIME 2

NOTE : G IS LOW THROUGHOUT WRITE CYCLE.

This write cycle time may be used for write and read in the same cycle (write followed by read).

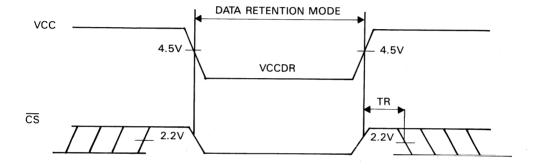

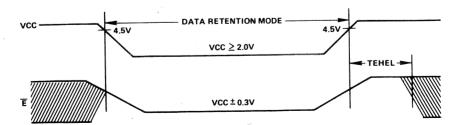

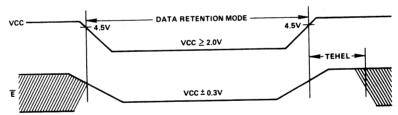

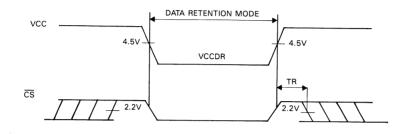

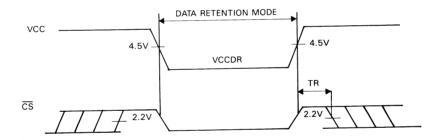

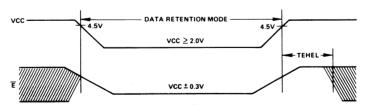

## Data retention Characteristics

| PARAMETER               | SYMBOL | TEST CONDITIONS                            |       |     |       | 16L<br>9 | 6116L<br>-2 |     | UNIT |

|-------------------------|--------|--------------------------------------------|-------|-----|-------|----------|-------------|-----|------|

|                         | ļ      |                                            | min   | max | min   | max      | min         | max | 1    |

| VCC for data retention  | VCCDR  | CS=VCC<br>VIN=OV or VCC                    | 2     | -   | 2     | _        | 2           | _   | ٧    |

| data retention current  | ICCDR  | VCC = 2.OV,<br>CS = VCC<br>VIN = OV or VCC | MAN   | 50  | _     | 200      | -           | 600 | μΑ   |

| operating recovery time | TR     |                                            | TAVAV |     | TAVAV |          | TAVAV       |     |      |

TAVAV = read cycle time

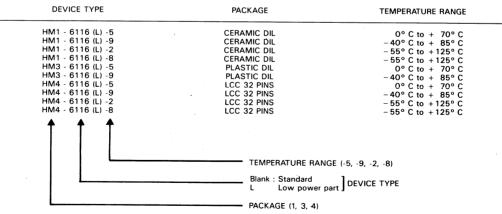

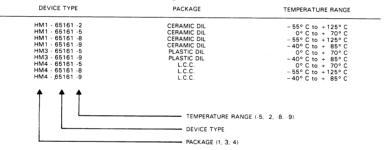

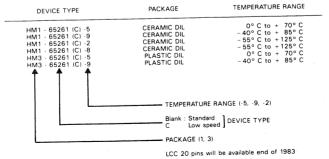

## **Ordering Information**

#### Specifications HM-6116 · HM-6116L

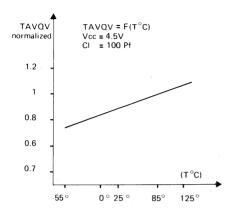

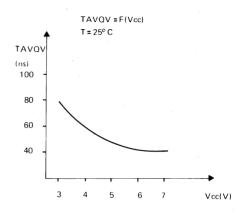

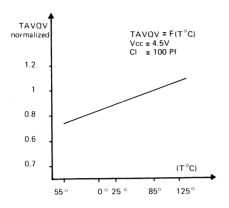

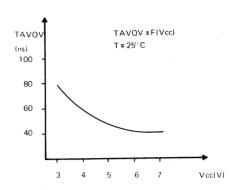

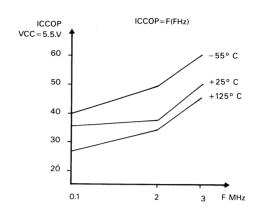

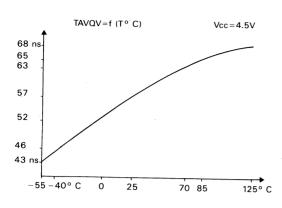

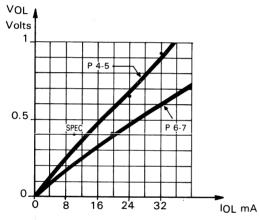

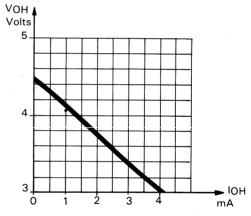

#### READ CYCLE TIME

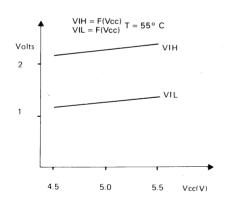

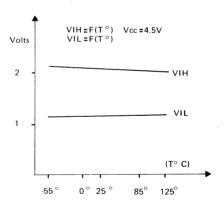

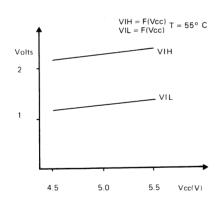

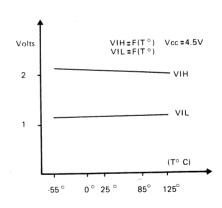

#### INPUT VOLTAGE

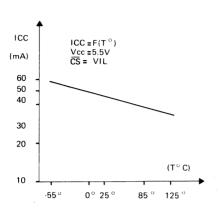

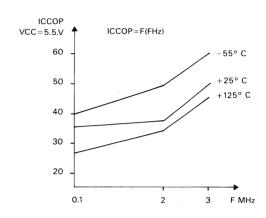

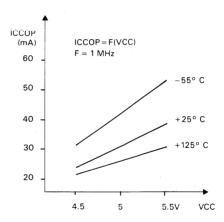

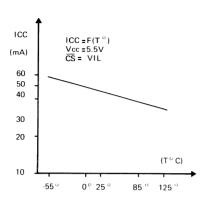

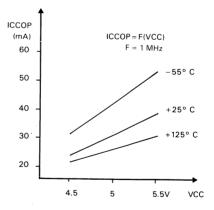

#### POWER SUPPLY CURRENT

2

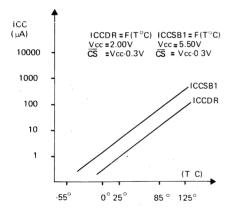

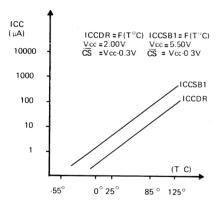

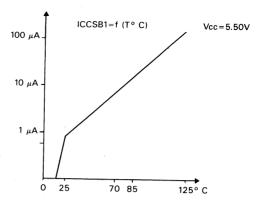

#### STANDBY AND DATA RETENTION CURRENT

# data sheet

#### Features

LOW POWER STANDBY

LOW POWER OPERATION

250μW MAX.

35mW/MHz MAX.

EXTREMELY LOW SPEED POWER PRODUCT

DATA RETENTION

@ 2.0V MIN.

- TTL COMPATIBLE INPUT/OUTPUT

- THREE-STATE OUTPUT

- STANDARD JEDEC PINOUT

- FAST ACCESS TIME

200nsec MAX.

- MILITARY TEMPERATURE RANGE

- INDUSTRIAL TEMPERATURE RANGE

- 18 PIN PACKAGE FOR HIGH DENSITY

- ON CHIP ADDRESS REGISTER

#### Description

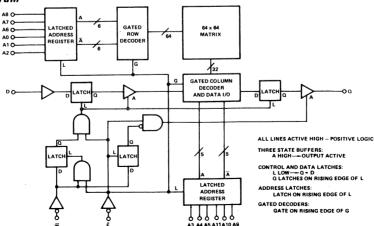

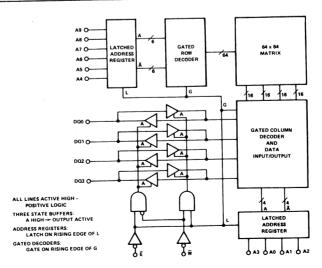

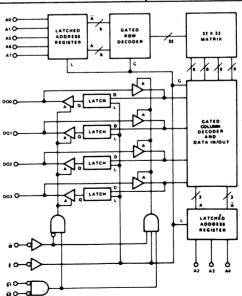

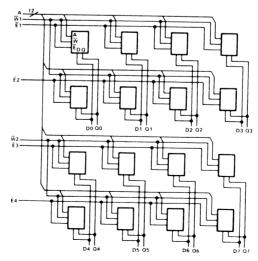

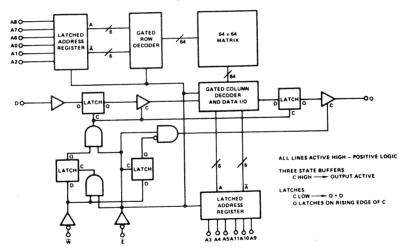

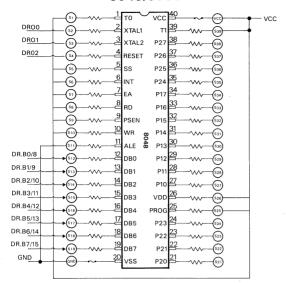

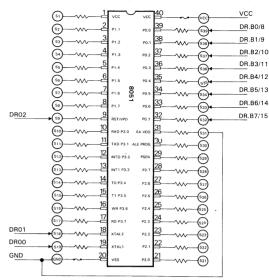

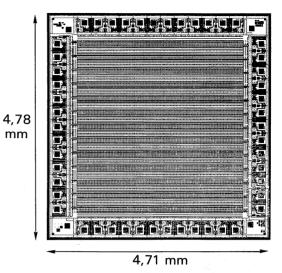

The HM-6504 is a 4096 x 1 static CMOS RAM fabricated using self aligned silicon gate technology. The device utilizes synchronous circuitry to achieve high performance and low power operation.

On chip latches are provided for addresses, data input and data output allowing efficient interfacing with microprocessor systems. The data output can be forced to a high impedance for use in expanded memory arrays.

The HM-6504 is a fully static RAM and may be maintained in any state for an indefinite period of time.

Data retention supply voltage and supply current are guaranteed over temperature.

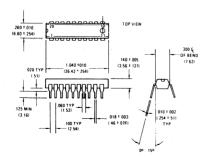

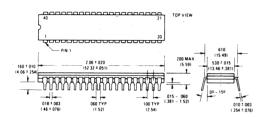

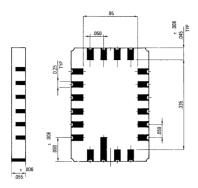

## **Pinout**

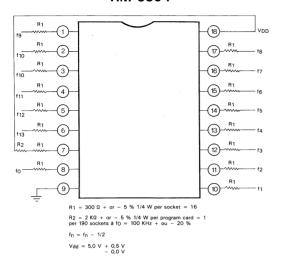

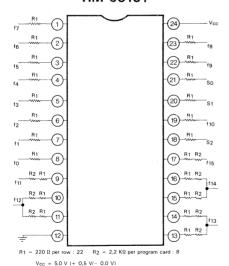

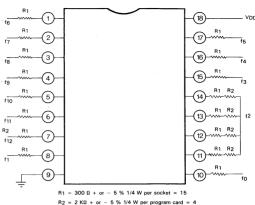

**HM-6504**

A0 10 18 7 VCC 17 TA6 A1 1 2 16 A7 A2 ∏3 дз П 4 15 A8 14 A9 A4 ∏ 5 13 A10 A5 ☐ 6 12 A11 Q[7 ωЦв 11 🛮 🖸

## Logic Symbol

10 D E

GND 0

## Functional Diagram

CAUTION: These devices are sensitive to electro-static discharge

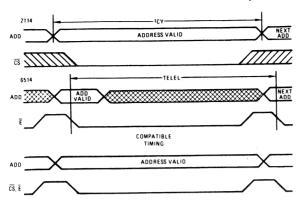

This data sheet utilizes a new set of specification nomenclature. This new format is an IEEE and JEDEC supported standard

All abbreviations use upper case letters with no subscripts. The initial symbol is one of these four characters:

- (Voltage)

- (Current)

- Р (Power)

- С (Capacitance)

The second letter specifies input (I) or output (O), and the third letter indicates the high (H), low (L) or off (Z) state of the pin during measurements. Examples:

VIL - Input Low Voltage

IOZ - Output Leakage Current

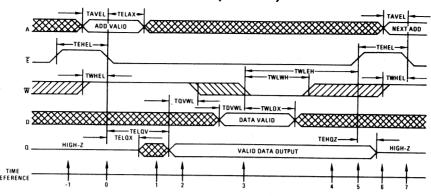

#### TIMING PARAMETER ABBREVIATIONS

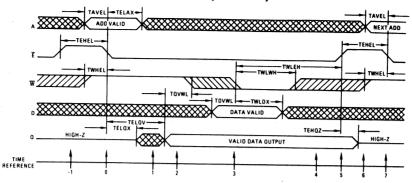

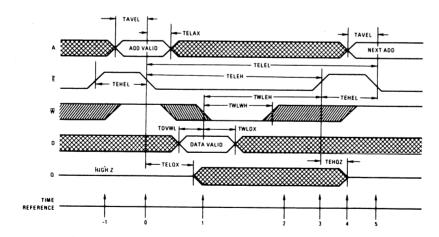

All timing abbreviations use upper case characters with no subscripts. The initial character is always T and is followed by four descriptors. These characters specify two signal points arranged in a "from-to" sequence that define a timing interval. The two descriptors for each signal point specify the signal name and the signal transitions. Thus the format is:

Signal name from which interval is defined Transition direction for first signal -Signal name to which interval is defined -Transition direction for second signal -

Signal Definitions:

A = Address

D = Data In-

Q = Data Out

W = Write Enable

E = Chip Enable

S = Chip Select

G = Output Enable

Transition Definitions:

H = Transition to High

L = Transition to Low

V = Transition to Valid

X = Transition to Invalid or Don't Care

Z = Transition to Off (High Impedance)

#### EXAMPLE:

The example shows Write pulse setup time defined as TWLEH-Time from Write enable Low to chip Enable High.

#### TIMING LIMITS

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address set-up time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time

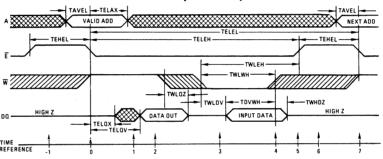

#### **WAVEFORMS**

| WAVEFORM<br>SYMBOL | INPUT                                  | OUTPUT                     |

|--------------------|----------------------------------------|----------------------------|

|                    | MUST BE<br>VALID                       | WILL BE<br>VALID           |

|                    | CHANGE<br>FROM H TO L                  | WILL CHANGE<br>FROM H TO L |

|                    | CHANGE<br>FROM L TO H                  | WILL CHANGE<br>FROM L TO H |

| <b>****</b>        | DON'T CARE:<br>ANY CHANGE<br>PERMITTED | CHANGING:<br>STATE UNKNOWN |

| $\rightarrow$      |                                        | HIGH<br>IMPEDANCE          |

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage - (VCC - GND)

-0.3V to +8.0V

Input or Output Voltage Applied

(GND -0.3V) to (VCC +0.3V)

Storage Temperature

-65°C to +150°C

#### **OPERATING RANGE**

Operating Supply Voltage Military (-2)

4.5V to 5.5V 4.5V to 5.5V

Industrial (-9)

Operating Temperature Military (-2) Industrial (-9)

-55°C to +125°C -40°C to +85°C

#### **ELECTRICAL CHARACTERISTICS**

|      |                                                       |                                                                                                                                                                                                                      | TEMP. 8                                               |             | TEMP = 250C 1                                 |                                  |                                      |

|------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------|-----------------------------------------------|----------------------------------|--------------------------------------|

|      |                                                       |                                                                                                                                                                                                                      | OPERA<br>RAM                                          |             | VCC = 5.0V                                    |                                  | 7507                                 |

|      | SYMBOL                                                | PARAMETER                                                                                                                                                                                                            | MIN                                                   | MAX         | TYPICAL                                       | UNITS                            | TEST<br>CONDITIONS                   |

|      | ICCSB                                                 | Standby Supply Current                                                                                                                                                                                               | 50                                                    |             | . 1.0                                         | μА                               | IO = 0<br>VI = VCC or GND            |

|      | ICCOP                                                 | Operating Supply Current (2)                                                                                                                                                                                         |                                                       | 7           | 5                                             | mA                               | f = 1MHz, IO = 0<br>VI = VCC or GND  |

|      | ICCDR                                                 | Data Retention Supply Current                                                                                                                                                                                        |                                                       | 25          | 0,1                                           | μА                               | VCC = 2.0, IO = 0<br>VI = VCC or GND |

|      | VCCDR                                                 | Data Retention Supply Voltage                                                                                                                                                                                        | 2.0                                                   |             | 1.4                                           | . V                              |                                      |

|      | 11                                                    | Input Leakage Current                                                                                                                                                                                                | -1.0                                                  | +1.0        | 0.0                                           | μΑ                               | GND ≤ VI ≤ VCC                       |

| D.C. | IIOZ                                                  | Input/Output Leakage Current                                                                                                                                                                                         | -1.0                                                  | +1.0        | 0.0                                           | μΑ                               | GND≤VIO≤VCC                          |

|      | VIL                                                   | Input Low Voltage                                                                                                                                                                                                    | -0.3                                                  | 0.8         | 2.0                                           | V                                |                                      |

|      | VIH                                                   | Input High Voltage                                                                                                                                                                                                   | VCC<br>-2.0                                           | VCC<br>+0.3 | 2.0                                           | V                                |                                      |

|      | VOL                                                   | Output Low Voltage                                                                                                                                                                                                   |                                                       | 0.45        | 0.35                                          | V                                | IO = 2.0mA                           |

|      | VOH                                                   | Output High Voltage                                                                                                                                                                                                  | 2.4                                                   |             | 4.0                                           | V                                | IO = -1.0mA                          |

|      | CI                                                    | Input Capacitance 3                                                                                                                                                                                                  |                                                       | 8.0         | 5.0                                           | pF                               | VI = VCC or GND<br>f = 1MHz          |

|      | CIO                                                   | Input/Output Capacitance ③                                                                                                                                                                                           | -                                                     | 10.0        | 6.0                                           | pF                               | VIO = VCC or GND<br>f = 1MHz         |

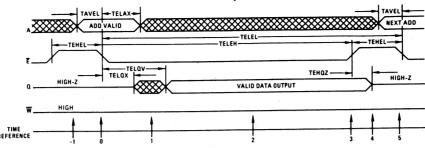

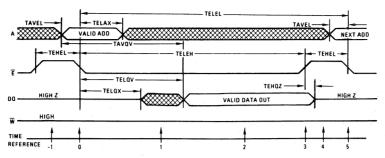

|      | TELQV                                                 | Chip Enable Access Time                                                                                                                                                                                              |                                                       | 200         | 150                                           | ns                               | 4                                    |

|      | VDVAT                                                 | Address Access Time                                                                                                                                                                                                  |                                                       | 220         | 150                                           | ns                               | 4                                    |

|      | TELQX                                                 | Chip Enable Output Enable<br>Time                                                                                                                                                                                    |                                                       | 80          | 40                                            | ns                               | (4)<br>(4)<br>(4)                    |

|      | TWLQZ                                                 | Write Enable Output Disable<br>Time                                                                                                                                                                                  | 20                                                    | 80          | 40                                            | ns                               | 4                                    |

|      | TEHQZ                                                 | Chip Enable Output Disable<br>Time                                                                                                                                                                                   |                                                       | 80          | 40                                            | ns                               | 4                                    |

|      |                                                       |                                                                                                                                                                                                                      |                                                       |             |                                               |                                  |                                      |

|      | TELEH                                                 | Chip Enable Pulse Negative<br>Width                                                                                                                                                                                  | 200                                                   |             | 150                                           | ns                               | 4                                    |

|      | TEHEL                                                 |                                                                                                                                                                                                                      | 200<br>90                                             |             | 150<br>60                                     | ns                               | 4                                    |

| A C  |                                                       | Width Chip Enable Pulse Positive                                                                                                                                                                                     |                                                       |             |                                               |                                  | 4                                    |

| A.C. | TEHEL                                                 | Width Chip Enable Pulse Positive Width                                                                                                                                                                               | 90                                                    |             | 60                                            | ns                               | 4                                    |

| A.C. | TEHEL<br>TAVEL                                        | Width Chip Enable Pulse Positive Width Address Setup Time                                                                                                                                                            | 90<br>20                                              |             | 60                                            | ns<br>ns                         | 4                                    |

| A.C. | TEHEL<br>TAVEL<br>TELAX                               | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time                                                                                                                                          | 90<br>20<br>50                                        |             | 60<br>0<br>20                                 | ns<br>ns<br>ns                   | 4                                    |

| A.C. | TEHEL<br>TAVEL<br>TELAX<br>TWLWH                      | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time Write Enable Pulse Width                                                                                                                 | 90<br>20<br>50<br>200                                 |             | 60<br>0<br>20<br>100                          | ns<br>ns<br>ns<br>ns             | 4                                    |

| A.C. | TEHEL TAVEL TELAX TWLWH TWLEH                         | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time Write Enable Pulse Width Write Enable Pulse Setup Time                                                                                   | 90<br>20<br>50<br>200<br>200                          |             | 60<br>0<br>20<br>100                          | ns<br>ns<br>ns<br>ns             | 4                                    |

| A.C. | TEHEL TAVEL TELAX TWLWH TWLEH TELWH                   | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time Write Enable Pulse Width Write Enable Pulse Setup Time Write Enable Pulse Hold Time                                                      | 90<br>20<br>50<br>200<br>200<br>200                   |             | 60<br>0<br>20<br>100<br>100                   | ns<br>ns<br>ns<br>ns<br>ns       | 4                                    |

| A.C. | TEHEL  TAVEL  TELAX  TWLWH  TWLEH  TELWH  TDVWH       | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time Write Enable Pulse Width Write Enable Pulse Setup Time Write Enable Pulse Hold Time Data Setup Time                                      | 90<br>20<br>50<br>200<br>200<br>200<br>120            |             | 60<br>0<br>20<br>100<br>100<br>150<br>80      | ns<br>ns<br>ns<br>ns<br>ns       | 4                                    |

| A.C. | TEHEL TAVEL TELAX TWLWH TWLEH TELWH TDVWH TWHDZ       | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time Write Enable Pulse Width Write Enable Pulse Setup Time Write Enable Pulse Hold Time Data Setup Time Data Hold Time                       | 90<br>20<br>50<br>200<br>200<br>200<br>120<br>0       |             | 60<br>0<br>20<br>100<br>100<br>150<br>80      | ns<br>ns<br>ns<br>ns<br>ns<br>ns | 4                                    |

| A.C. | TEHEL TAVEL TELAX TWLWH TWLEH TELWH TDVWH TWHDZ TWLDV | Width Chip Enable Pulse Positive Width Address Setup Time Address Hold Time Write Enable Pulse Width Write Enable Pulse Setup Time Write Enable Pulse Hold Time Data Setup Time Data Hold Time Write Data Delay Time | 90<br>20<br>50<br>200<br>200<br>200<br>120<br>0<br>80 |             | 60<br>0<br>20<br>100<br>100<br>150<br>80<br>0 | ns<br>ns<br>ns<br>ns<br>ns<br>ns |                                      |

NOTES: 1

All devices tested at worst case limits. Room Temp., 5V data provided for information - not guaranteed. Operating Supply Current (ICCOP) is proportional to Operating Frequency. Ex: Typical ICCOP = 5mA/MHz.

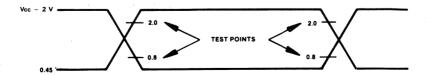

Capacitance sampled and guaranteed - not 100% tested. AC test conditions: Inputs - TRISE = TFALL = 20ns; Output - CLOAD = 50pF. All timing measured at 1.5V reference level.

#### **ABSOLUTE MAXIMUM RATINGS**

**OPERATING RANGE**

Supply Voltage - (VCC -GND)

-0.3V to +8.0V

Input or Output Voltage Applied

(GND -0.3V) to (VCC +0.3V)

Storage Temperature

-65°C to +150°C

Operating Supply Voltage Military (-2) Industrial (-9)

4.5V to 5.5V 4.5V to 5.5V

Operating Temperature Military (-2) Industrial (-9)

-55°C to +125°C -40°C to +85°C

#### **ELECTRICAL CHARACTERISTICS**

|        | ·                                      |             |                                |                             |       |                                                             |

|--------|----------------------------------------|-------------|--------------------------------|-----------------------------|-------|-------------------------------------------------------------|

|        |                                        | OPE         | P. & VCC =<br>ERATING<br>RANGE | TEMP = 25°C 1<br>VCC = 5.0V |       |                                                             |

| SYMBOL | PARAMETER                              | MIN         | MAX                            | TYPICAL                     | UNITS | TEST<br>CONDITIONS                                          |

| ICCSB  | Standby Supply Current                 |             | 50                             | 1.0                         | μА    | IO = 0<br>VI = VCC or GND                                   |

| ICCOP  | Operating Supply Current 2             |             | 7                              | 5                           | mA    | f = 1MHz, IO = 0<br>VI = VCC or GND                         |

| ICCDR  | Data Retention Supply Current          |             | 25                             | 0.1                         | μΑ    | 10 = 0, VCC = 2.0                                           |

| VCCDR  | Data Retention Supply Voltage          | 2.0         |                                | 1.4                         | v     | VI = VCC or GND                                             |

| 11     | Input Leakage Current                  | -1.0        | +1.0                           | 0.0                         | μΑ    | GND≤VI≤VCC                                                  |

| IOZ    | Output Leakage Current                 | -1.0        | +1.0                           | 0.0                         | μΑ    | GND≤vo <vcc< td=""></vcc<>                                  |

| VIL    | Input Low Voltage                      | -0.3        | 0.8                            | 2.0                         | v     |                                                             |

| VIH    | Input High Voltage                     | VCC<br>-2.0 | +0.3                           | 2.0                         | v     |                                                             |

| VOL    | Output Low Voltage                     | 1           | 0.4                            | 0.25                        | v     | IO = 2.0mA                                                  |

| VOH    | Output High Voltage                    | 2.4         |                                | 4.0                         | v     | IO = -1.0mA                                                 |

| CI     | Input Capacitance 3                    |             | 8.0                            | 5.0                         | ρF    | f = 1MHz<br>VI = VCC or GND                                 |

| CO     | Output Capacitance (3)                 |             | 10.0                           | 6.0                         | рF    | f = 1MHz<br>VO = VCC or GND                                 |

| TELQV  | Chip Enable Access Time                |             | 300                            | 170                         | ns    | <b>A</b>                                                    |

| TAVQV  | Address Access Time                    |             | 320                            | 170                         | ns    | <u> </u>                                                    |

| TELQX  | Chip Enable Output Enable<br>Time      | 20          | 100                            | 40                          | ns    | (4)<br>(4)<br>(4)                                           |

| TEHQZ  | Chip Enable Output Disable<br>Time     |             | 100                            | 40                          | ns    | 4                                                           |

| TELEH  | Chip Enable Pulse Negative<br>Width    | 300         |                                | 170                         | ns    | 4                                                           |

| TEHEL  | Chip Enable Pulse Positive<br>Width    | 120         |                                | 70                          | ns    | 4                                                           |

| TAVEL  | Address Setup Time                     | 20          |                                | 0                           | ns    | <b>(4)</b>                                                  |

| TELAX  | Address Hold Time                      | 50          |                                | 20                          | ns    | <u>(4)</u>                                                  |

| TWLWH  | Write Enable Pulse Width               | 80          |                                | 40                          | ns    | <u>ŏ</u>                                                    |

| TWLEH  | Write Enable Pulse Setup Time          | 200         |                                | 130                         | ns    | <u>(4)</u>                                                  |

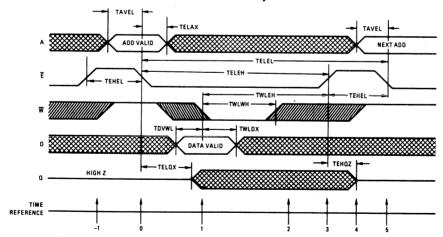

| TWLEL  | Early Write Pulse Setup Time           | 0           |                                | -10                         | ns    | <u>(4)</u>                                                  |

| TWHEL  | Write Enable Read Mode ;<br>Setup Time | 0           |                                | -10                         | ns    | <ul><li>4</li><li>4</li><li>4</li><li>4</li></ul>           |

| TELWH  | Early Write Pulse Hold Time            | 80          |                                | 40                          | ns    | 4                                                           |

| TDVWL  | Data Setup Time                        | 0           |                                | 0                           | ns    | <ul><li>4</li><li>4</li><li>4</li><li>4</li><li>4</li></ul> |

| TDVEL  | Early Write Data Setup Time            | 0           | .                              | 0                           | ns    | <u>.</u>                                                    |

| TWLDX  | Data Hold Time                         | 80          |                                | 40                          | ns    | <u>.</u>                                                    |

| TELDX  | Early Write Data Hold Time             | 80          |                                | 40                          | ns    | (4)                                                         |

|        |                                        |             |                                | 1                           |       | •                                                           |

A.C.

D.C.

TQVWL

TELEL

- NOTES: 1. All devices tested at worst case limits. Room temp., 5 volt data provided for information not guaranteed.

- 2. Operating Supply Current (ICCOP) is proportional to Operating Frequency. Example: Typical ICCOP = 5mA/MHz.

- 3. Capacitance sampled and guaranteed not 100% tested.

Data Valid to Write Time

Read or Write Cycle Time

AC Test Conditions: Inputs - TRISE = TFALL = 20nsec; Outputs - CLOAD = 50pF. All timing measurements at 1.5V reference level.

0

2-14

## Specifications HM-6504C-9

## **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage - (VCC -GND)

-0.3V to +8.0V

Input or Output Voltage Applied

(GND -0.3V) to (VCC +0.3V)

Storage Temperature

-65°C to +150°C

### OPERATING RANGE

Operating Supply Voltage Industrial (-9)

4.5V to 5.5V

Operating Temperature Industrial (-9)

-40°C to +85°C

### **ELECTRICAL CHARACTERISTICS**

D.C.

|        |                                      | OPE         | . & VCC =<br>RATING<br>ANGE | TEMP = 25°C 1<br>VCC = 5.0V |       | TEST                                   |

|--------|--------------------------------------|-------------|-----------------------------|-----------------------------|-------|----------------------------------------|

| SYMBOL | PARAMETER                            | MIN         | MAX                         | TYPICAL                     | UŅITS | CONDITIONS                             |

| ICCSB  | Standby Supply Current               |             | 100                         | 10                          | μА    | IO = 0<br>VI = VCC or GND              |

| ICCOP  | Operating Supply Current 2           |             | 7                           | 5                           | mA    | f = 1MHz, IO = 0<br>VI = VCC or GND    |

| ICCDR  | Data Retention Supply Current        |             | 50                          | 25                          | μА    | IO = 0 VCC = 2.0V<br>VI = VCC or GND   |

| VCCDR  | Data Retention Supply Voltage        | 2.0         |                             | 1.4                         | V     |                                        |

| П      | Input Leakage Current                | -1.0        | +1.0                        | 0.0                         | μΑ    | GND≤VI≤VCC                             |

| IOZ    | Output Leakage Current               | -1.0        | +1.0                        | 0.0                         | μΑ    | GND≤VO≤VCC                             |

| VIL    | Input Low Voltage                    | -0.3        | 0.8                         | 2.0                         | V     |                                        |

| VIH    | Input High Voltage                   | VCC<br>-2.0 | VCC<br>+0.3                 | 2.0                         | V     |                                        |

| VOL    | Output Low Voltage                   | 2.0         | 0.4                         | 0.25                        | V     | 10 = 2.0mA                             |

| VOH    | Output High Voltage                  | 2.4         |                             | 4.0                         | V     | IO = -1.0mA                            |

| CI     | Input Capacitance ③                  |             | 8.0                         | 5.0                         | pF    | f = 1MHz<br>VI = VCC or GND            |

| co     | Output Capacitance 3                 |             | 10.0                        | 6.0                         | ρF    | f = 1MHz<br>VO= VCC or GND             |

| TELQV  | Chip Enable Access Time              |             | 300                         | 170                         | ns    | 4                                      |

| TAVQV  | Address Access Time                  |             | 320                         | 170                         | ns    | 4                                      |

| TELQX  | Chip Enable Output Enable            | 20          | 100                         | 40                          | ns    | (4)<br>(4)                             |

| TEHQZ  | Chip Enable Output Disable           |             | 100                         | 40                          | ns    | 4                                      |

| TELEH  | Chip Enable Pulse Negative<br>Width  | 300         |                             | 170                         | ns    | 4                                      |

| TEHEL  | Chip Enable Pulse Positive<br>Width  | 120         |                             | 70                          | ns    | 4                                      |

| TAVEL  | Addréss Setup Time                   | 20          |                             | 0                           | ns    | 4                                      |

| TELAX  | Address Hold Time                    | 50          |                             | 20                          | ns    | 4                                      |

| TWLWH  | Write Enable Pulse Width             | 80          |                             | 40                          | ns    | 4                                      |

| TWLEH  | Write Enable Pulse Setup Time        | 200         |                             | 130                         | ns    | 4                                      |

| TWLEL  | Early Write Pulse Setup Time         | 0           |                             | -10                         | ns    | 4                                      |

| TWHEL  | Write Enable Read Mode<br>Setup Time | 0           |                             | -10                         | ns    | •••••••••••••••••••••••••••••••••••••• |

| TELWH  | Early Write Pulse Hold Time          | 80          |                             | 40 .                        | ns    | 4                                      |

| TDVWL  | Data Setup Time                      | 0           |                             | 0                           | ns    | 4                                      |

| TDVEL  | Early Write Data Setup Time          | 0           | 1                           | 0                           | ns    | 4                                      |

| TWLDX  | Data Hold Time                       | 80          |                             | 40                          | ns    | 4                                      |

| TELDX  | Early Write Data Hold Time           | 80          |                             | 40                          | ns    | 4                                      |

| TQVWL  | Data Valid to Write Time             | 0           |                             | 0                           | ns    | 4                                      |

| TELEL  | Read or Write Cycle Time             | 420         |                             | 240                         | ns    | 4                                      |

A.C.

NOTES: 1. All devices tested at worst case limits. Room temp., 5 volt data provided for information - not guaranteed.

2. Operating Supply Current (ICCOP) is proportional to Operating Frequency. Example: Typical ICCOP = 5mA/MHz.

3. Capacitance sampled and guaranteed - not 100% tested.

AC Test Conditions: Inputs – TRISE = TFALL = 20nsec; Outputs – CLOAD = 50pF. All timing measurements at 1.5V reference level.

## **ABSOLUTE MAXIMUM RATINGS**

**OPERATING RANGE**

Supply Voltage - (VCC - GND)

-0.3V to +8.0V

Input or Output Voltage Applied

(GND -0.3V) to (GND +0.3V)

Storage Temperature

-65°C to +150°C

Operating Supply Voltage

Commercial

4.5V to 5.5V

Operating Temperature Commercial

0°C to +75°C

### **ELECTRICAL CHARACTERISTICS**

|        |                                     | OPE         | . & VCC =<br>RATING<br>ANGE |    | TEMP = 25°C 1<br>VCC = 5.0V |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-------------------------------------|-------------|-----------------------------|----|-----------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|